This block is similar to the Hold block. The only difference is that simulated real-world effects are applied on the clocked input signal u before transforming the signal to a continuous-time signal with a zero-order hold. In particular:

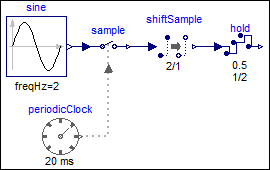

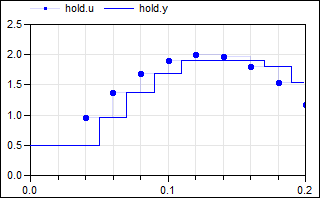

The following example samples a sine signal with an amplitude of 2.0 with a periodic clock of 20 ms period and delays it for 2 sample periods. The resulting signal is hold with the HoldWithDAeffects block. As a result, the clock of hold.u starts ticking at 40 ms. The output hold.y of the block is a continuous-time signal that is present from the start of the simulation. Before the first tick of the clock of hold.u, it is set to 0.5 (= the value of parameter hold.y_start). Additionally, the following effects are added to the hold block:

|

|

|

| model | simulation result |

Due to the limitation of the output signal, the values of hold.u ≥

1.9 are limited to 1.9.

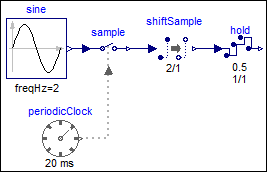

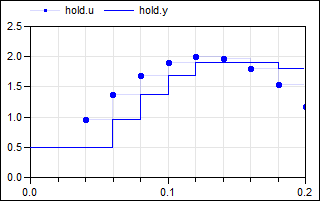

If the hold output is delayed by one sample period, then the

previous(…) value of the input is output, and the

first tick is delayed by one sample period, as shown by the

modified example from above:

|

|

|

| model | simulation result |

Note, the computational delay of one sample period is defined by

shiftCounter=1, resolution=1, as shown in the icon of the hold

block.