Example model for signal ranker

Example that demonstrates the use of the signal ranker model.

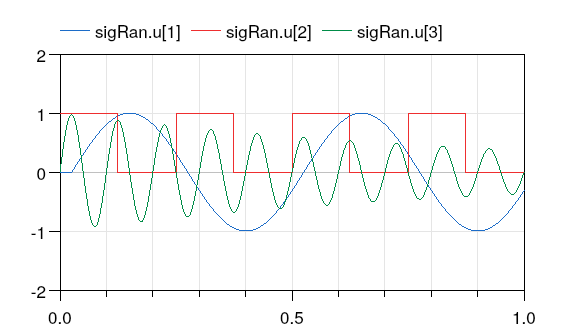

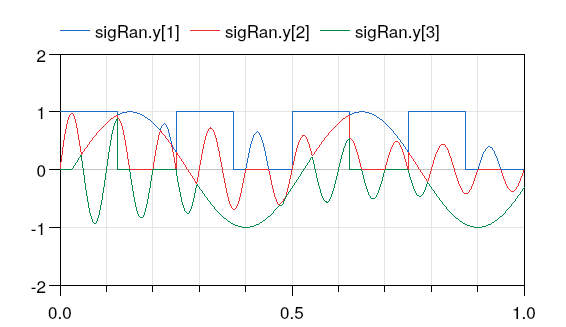

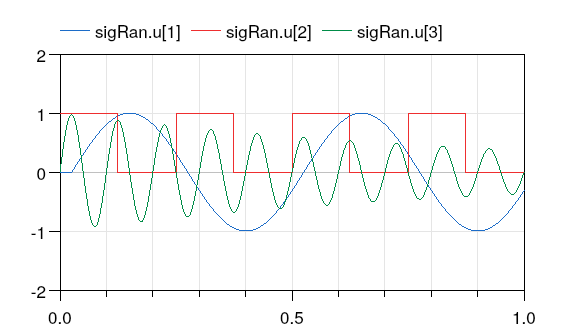

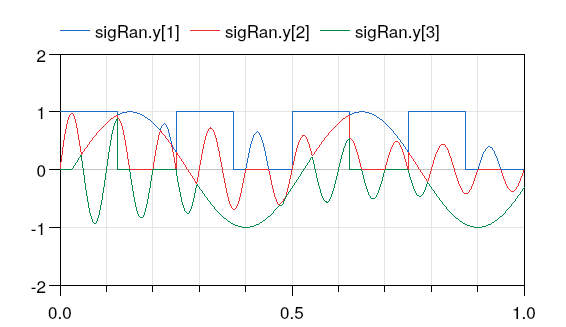

The figure below shows the input and output signals of the block.

Note that sigRan.y[1] ≥ sigRan.y[2] ≥ sigRan.y[3].

- October 15, 2021, by Michael Wetter:

Moved start time of sine input signal to avoid simultaneous state

event and time event.

This is for IBPSA,

#1534.

- November 21, 2011, by Michael Wetter:

Added documentation.

Generated at 2026-04-30T18:19:17Z by OpenModelicaOpenModelica 1.26.5 using

GenerateDoc.mos