This block assigns a clock to the Real input signal u and provides u as output signal y.

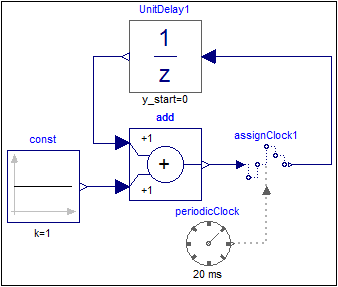

The following example

shows a discrete counter. In order to execute the counter with a

sample period of 20ms an AssignClock block is used. Due to clock

inference all equations within the blocks are deduced to be active

at the clock ticks given by the periodicClock block.

|

|

|

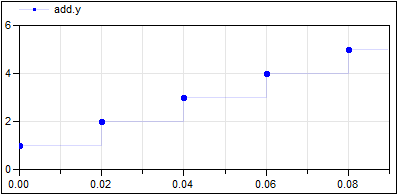

| model | simulation result |

At every clock tick (that is at every 20ms) the output of the unitDelay1 block is incremented by one.

| Date | Author | Company/Institute | Comment |

|---|---|---|---|

| 2012-08-20 | Bernhard Thiele | DLR, Institute for System Dynamics and Control | Initial version |