This block holds the clocked Real input signal u with a zero order hold and provides it as continuous-time output signal y. The clock of the input signal is inferred (that is, it needs to be defined somewhere else in the clocked partition).

To be more precise: The input signal u(ti) must be a clocked signal. The output signal y(t) is a piecewise constant continuous-time signal. When the clock of u ticks at time ti, the block output y(ti) = u(ti). Otherwise y(t), t ≥ti, is the value of u(ti) from the last clock activation at time ti. Before the first clock activation of u, the block outputs the value of parameter y_start. The value of this parameter is displayed below the icon.

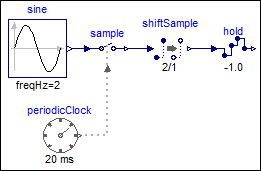

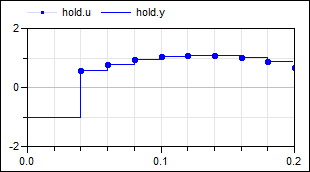

The following

example samples a sine signal with a periodic clock of 20 ms

period and delays it for 2 sample periods. The resulting signal is

hold with the Hold block. As a result, the clock of hold.u starts

ticking at 40 ms. The output hold.y of the block is a

continuous-time signal that is present from the start of the

simulation. Before the first tick of the clock of hold.u, it is set

to -1.0 (= the value of parameter hold.y_start).

|

|

|

| model | simulation result |