Note, it does not make much sense to vectorize this block, because then also the clock input is vectorized. Instead, if the input signal is a vector, use block SampleVectorizedAndClocked that has a vector Real input and output, as well as a scalar clock input.

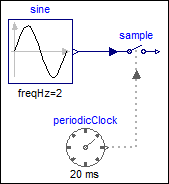

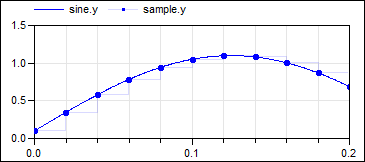

The following

example samples a sine signal with a periodic clock of 20 ms

period:

|

|

|

| model | simulation result |